|

Рефератырусскому языку полиграфия хозяйство |

Реферат: Большие интегральные схемыРеферат: Большие интегральные схемыМинистерство образования и науки Республики Казахстан Карагандинский государственный технический университет Кафедра ______ ________ РЕФЕРАТ по дисциплине: Организация вычислительных систем Тема: Большие интегральные схемы Руководитель _________________ (оценка) (фамилия, инициалы) (подпись) (дата) Студент (группа) (фамилия, инициалы) (подпись) (дата)

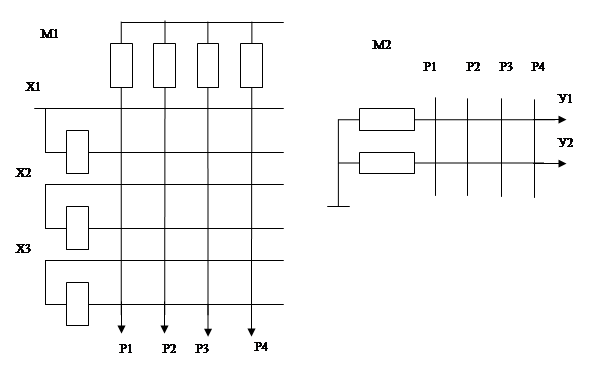

2009 Одним из важнейших путей совершенствования вычислительной техники является широкое применение в ней достижений современной микроэлектроники. Успехи полупроводниковой интегральной электроники привели к созданию нового класса сложных функциональных электронных изделий - больших интегральных схем, которые стали основной элементной базой ЭВМ четвертого поколения (конец 70-х годов). В одной такой схеме объёмом всего лишь в доли кубического сантиметра размещается блок, занимавший в ЭВМ первого поколения целый шкаф. В результате достигнуто существенное повышение производительности ЭВМ. Если в ЭВМ третьего поколения быстродействие достигает 20-30 млн операций в секунду, то в машинах четвёртого поколения производительность достигает сотен миллионов операций в секунду. Соответственно возрастает и объём памяти. Наряду с усовершенствованием традиционных устройств памяти на магнитных дисках и лентах создаётся память без движущихся частей. Общий объём внешней памяти в крупных машинах четвёртого поколения превосходит 1014 символов, что эквивалентно библиотеке, состоящей из нескольких миллионов объёмистых томов. БИС созданы в результате естественного развития интегральных схем. Предпосылкой их появления является освоение электронной промышленностью планарной технологии изготовления кремниевых полупроводниковых приборов. Принципиальная новизна этой технологии состоит в том, что она позволила заменить обычные дискретные компоненты диффузионными или тонкоплёночными компонентами. Высокая надежность ЭВМ закладывается в процессе ее производства. Переход на новую элементную базу - сверхбольшие интегральные схемы (СБИС) - резко сокращает число используемых интегральных схем, а значит, и число их соединений друг с другом. Хорошо продуманы компоновка компьютера и обеспечение требуемых режимов работы (охлаждение, защита от пыли). Все современные вычислительные машины строятся на комплексах (системах) интегральных микросхем (ИС). Электронная микросхема называется интегральной, если ее компоненты и соединения между ними выполнены в едином технологическом цикле, на едином основании и имеют общую герметизацию и защиту от механических воздействий. Каждая микросхема представляет собой миниатюрную электронную схему, сформированную послойно в кристалле полупроводника: кремния, германия и т.д. В состав микропроцессорных наборов включаются различные типы микросхем, но все они должны иметь единый тип межмодульных связей, основанный на стандартизации параметров сигналов взаимодействия (амплитуда, полярность, длительность импульсов и т.п.). Основу набора обычно составляют большие интегральные схемы (БИС) и сверхбольшие интегральные схемы (СБИС). В ближайшем будущем следует ожидать появления ультрабольших ИС (УБИС). Кроме них обычно используются микросхемы с малой и средней степенью интеграции (СИС). Функционально микросхемы могут соответствовать устройству, узлу или блоку, но каждая из них состоит из комбинации простейших логических элементов, реализующих функции формирования, преобразования, запоминания сигналов и т.д. Все современные ЭВМ строятся на микропроцессорных наборах, основу которых составляют большие (БИС) и сверхбольшие интегральные схемы (СБИС). Технологический принцип разработки и производства интегральных схем действует уже более четверти века. Он заключается в послойном изготовлении частей электронных схем по циклу "программа - рисунок - схема". По программам на запыленный фоторезисторный слой наносится рисунок будущего слоя микросхемы. Затем рисунок протравливается, фиксируется, закрепляется и изолируется от новых слоев. На основе этого создается пространственная твердотельная структура. Например, СБИС типа Pentium включает около трех с половиной миллионов транзисторов, размещаемых в пятислойной структуре. Степень микроминиатюризации, размер кристалла ИС, производительность и стоимость технологии напрямую определяются типом литографии. До настоящего времени доминирующей оставалась оптическая литография, т.е. послойные рисунки на фоторезисторе микросхем наносились световым лучом. В настоящее время ведущие компании, производящие микросхемы, реализуют кристаллы с размерами примерно 400-600 мм2 для процессоров (например, Pentium) и 200-400 мм2 - для схем памяти. Минимальный топологический размер (толщина линий) при этом составляет 0,25-0,135 мкм. Для сравнения можно привести такой пример. Толщина человеческого волоса составляет примерно 100 мкм. Значит, при таком разрешении на толщине 100 мкм требуется вычерчивать более двухсот линий. Дальнейшие успехи микроэлектроники связываются с электронной (лазерной), ионной и рентгеновской литографией. Это позволяет выйти на размеры 0,13; 0,10 и даже 0,08 мкм. Вместо ранее используемых алюминиевых проводников в микросхемах повсеместно начинают применять медные соединения, что позволяет повысить частоту работы. Такие высокие технологии порождают целый ряд проблем. Микроскопическая толщина линий, сравнимая с диаметром молекул, требует высокой чистоты используемых и напыляемых материалов, применения вакуумных установок и снижения рабочих температур. Действительно, достаточно попадания мельчайшей пылинки при изготовлении микросхемы - и она попадает в брак. Поэтому новые заводы по производству микросхем представляют собой уникальное оборудование, размещаемое в "чистых помещениях класса 1", микросхемы в которых транспортируются от оборудования к оборудованию в замкнутых сверхчистых мини-атмосферах класса 1000. Мини-атмосфеpa создается, например, сверхчистым азотом или другим инертным газом при давлении КГ4 Торр. В настоящее время основой построения всех микросхем была и остается КМоп-технология (комплементарные схемы, т.е. совместно использующие п- и р-переходы в транзисторах со структурой "металл - окисел - полупроводник"). Однако появление БИС породило очень серьезную проблему-"что положить на подложку" или, другими словами, каким образом реализовать устройство на схемах с таким колоссальным количеством элементов. Первым и довольно естественным решением этой проблемы явилось изготовление так называемых заказных схем, разрабатываемых каждый раз специально для использования в конкретной аппаратуре. В то же время проектирование заказных БИС - весьма длительный и трудоемкий процесс, использующий сложные человеко-машинные системы автоматизированного проектирования. Поэтому разработка и изготовление заказных БИС могут быть экономически оправданы только при массовом производстве аппаратуры, в которой эти схемы применяются. Хорошей альтернативой заказным БИС явились микропроцессорные наборы - совокупность больших интегральных схем, реализующих сложные функции цифровой аппаратуры. Из этих "кирпичей" достаточно просто строятся микрокомпьютеры (микро-ЭВМ), получившие исключительное развитие и нашедшие широкое применение в разнообразных системах управления. Микропроцессор является универсальным устройством, способным реализовать любую логическую функцию. Однако программная реализация логики управления осуществляется сравнительно медленно, микропроцессор зачастую не способен обеспечить необходимое быстродействие. В связи с этим в настоящее время широкое распространение получили программируемые БИС с матричной структурой, среди которых особое место занимают программируемые логические матрицы (ПЛМ) - большие интегральные схемы, сочетающие регулярность структуры полупроводникового запоминающего устройства (ЗУ) с универсальностью микропроцессора. ПЛМ обладает существенными преимуществами перед микропроцессором при реализации сложных алгоритмов управления. В качестве функциональных узлов БИС, ориентированных на реализацию булевых функций, широко используются так называемые матричные схемы. Матричная схема представляет собой сетку ортогональных проводников, в местах пересечения которых могут быть установлены полупроводниковые элементы с односторонней проводимостью (ЭОП) - диоды или транзисторы. Рассмотрим матрицы М1и М2 на рисунке №1. Способ включения ЭОП в местах пересечения шин матрицы М1 позволяет реализовать на любом из е выходов любую конъюнкцию её входных переменных, взятых со знаком либо без знака инверсии. Р4

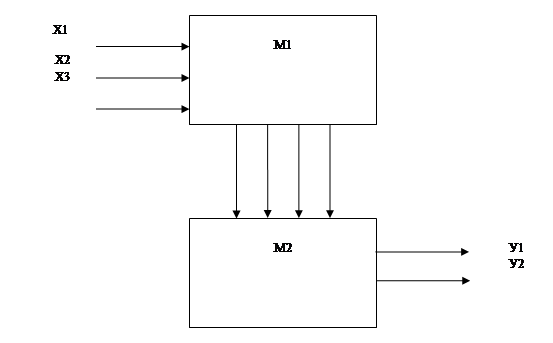

Рисунок №1 Матрица М2 имеет 4 вертикальных и 2 горизонтальных шины. Способ включения ЭОП в местах пересечения шин М2 позволяет реализовать на любом из е выходов любую дизъюнкцию её входных переменных. Если соединить эти матрицы как показано на рисунке №2, то можно заметить, что любая система булевых функций у1. yn водных переменных x1. xn может быть реализована двухуровневой матричной схемой, на первом уровне которой образуются различные элементарные конъюнкции, а на втором - дизъюнкции соответствующих конъюнкций (y1…yn). В итоге построение схем с матричной структурой сводится к определению точек пересечения шин, где должны быть включены ЭОП.

Рисунок №2 По способу программирования различают матрицы, настраиваемые (программируемые) на заводе-изготовителе, пользователем и репрограммируемые (многократно настраиваемые). В матрицах первого типа соединение ЭОП с шинами осуществляется 1 раз с помощью специальных масок, используемых для металлизации определённых участков кристалла БИС. После изготовления БИС полученные соединения изменены быть не могут. Матрицы второго типа поставляются потребителю не настроенными и содержащими ЭОП в каждой точке пересечения их шин. Настройка сводится к удалению (отключению) некоторых ненужных ЭОП. Физически процесс настройки осуществляется различными способами, например, путём пропускания серии импульсов тока достаточно большой амплитуды через соответствующий ЭОП и разрушения плавкой перемычки, включённой последовательно с этим ЭОП и соединяющей его с одной из шин в точке их пересечения. Матрицы третьего типа позволяют осуществлять программирование неоднократно. Повторное программирование выполняется электрическим способом после стирания содержимого матриц под действием ультрафиолетового (иногда рентгеновского) облучения или электрическим способом отдельно для каждого ЭОП. Так же необходимо сказать несколько слов о так называемых программируемых матрицах. Программируемая логическая матрица (ПЛМ) представляет собой функциональный блок, созданный на базе полупроводниковой технологии и предназначенный для реализации логических схем цифровых систем. В зависимости от внутренней организации программируемые логические матрицы можно разделить на ПЛМ комбинационной логики и ПЛМ с памятью. Следует отметить, что на кристалле БИС ПЛМ предусмотрена специальная система шин, позволяющая соединять выходы донной матрицы с входами другой. Выполнение разрезов шин и организация необходимых связей между входами и выходами различных матриц осуществляются на этапе настройки ПЛМ на заводе изготовителе. |